#### UNIVERSITY OF MINNESOTA

| This is to certify that I have examined this copy of a doctoral Dissertation by                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cristinel Ababei                                                                                                                                              |

| and have found that it is complete and satisfactory in all respects, and that any and all revisions required by the final examining committee have been made. |

|                                                                                                                                                               |

| Name of Faculty Adviser                                                                                                                                       |

|                                                                                                                                                               |

| Signature of Faculty Adviser                                                                                                                                  |

|                                                                                                                                                               |

| Date                                                                                                                                                          |

GRADUATE SCHOOL

# Design Automation for Physical Synthesis of VLSI Circuits and FPGAs

A DISSERTATION

SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL

OF THE UNIVERSITY OF MINNESOTA

BY

Cristinel Ababei

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHYLOSOPHY

Kia Bazargan

December 2004

## **Acknowledgements**

First of all, I would like to thank my research advisor Prof. Kia Bazargan for his guidance, positive spirit, and invaluable support throughout the course of my study and work at the University of Minnesota. He has always been a source of encouragement, and his spirit, ideas, and personality have been great sources of inspiration.

I would like to thank Prof. George Karypis, Prof. Sachin Sapatnekar, and Prof. Gerald Sobelman for serving on my Preliminary Oral Examination and dissertation committees and for their constructive feedback.

During the course of my study at the University of Minnesota, I had the opportunity to meet and interact with many talented and interesting people from whom I learned many things and who, in one way or another, contributed to my work and sometimes changed the way I see things today.

I had a great collaboration with Navaratnasothie Selvakkumaran and Prof. George Karypis. I admired their hard-work and can-be-done attitude.

I would like to thank Prof. Igor Markov of the University of Michigan for his many prompt and helpful answers to my questions regarding the Capo placer. Generally, I would like to thank the EDA community and its researchers, whose many papers that I read shaped my ideas and research directions.

I was fortunate to be a graduate student at UMN and I will always be fond of Minnesota.

I would like to thank the other members in my group as well as the members of Prof. Sachin Sapatnekar's group (VEDA Lab.) for creating an excellent research and social environment. I would especially like to thank Kartikeyan Bhasyam, Wonjoon Choi, Pongstorn Maidee, and Hushrav Mogal for many interesting discussions and their collaboration. I would also like to thank Mahesh Ketkar and Arvind Karandikar my oldest friends and colleagues from the VEDA Lab. Also, Rupesh Shelar, Venkat Rajappan, Anup Sultania, Jaskirat Singh, Vidyasagar Nookala, Hongliang Chang, and Brent Goplen have been great people I interacted with.

I thank Radu Marculescu for his constant guidance even when he was far away.

It is hard to voice my thanks and gratitude to my parents for their love and sacrifices throughout all my schooling endeavors. My siblings Marcel and Angelica never stopped encouraging me.

There are no words to express my thanks to my wife Anca for her unconditional love and faith in me. She was my biggest fan and my main source of encouragement and support for all these years since we first met in Iasi, our college town.

Finally, I would like to acknowledge the financial support provided by the ECE Department at the University of Minnesota, my advisor Prof. Kia Bazargan, ACM, and IEEE.

To Anca

### **Abstract**

We address the problem of delay optimization for VLSI circuits and FPGAs at the physical design stage. A new net-based statistical timing-driven partitioning algorithm demonstrates that circuit delay can be improved while the run-time remains virtually the same and the cutsize deterioration is insignificant. Because path-based timing-driven partitioning has the advantage that global information about the structure of the circuit is captured, we also propose multiobjective partitioning for cutsize and circuit delay minimization. We change the partitioning process itself by introducing a new objective function that incorporates a truly path-based delay component for the most critical paths. To avoid semi-critical paths from becoming critical, the traditional slack-based delay component is also accounted for. The proposed timing-driven partitioning algorithm is built on top of the hMetis algorithm, which is very efficient. Simulations results show that important delay improvements can be obtained. Integration of our partitioning algorithms into a leading-edge placement tool demonstrates the ability of the proposed edgeweighting and path-based approaches for partitioning to lead to a better circuit performance. We propose and develop means for changing a standard timing-driven partitioning-based placement algorithm in order to design more predictable (predictability is to be achieved in the face of design uncertainties) and robust (high robustness means that performance of the design is less influenced by noise factors and remains within acceptable limits) circuits without sacrificing much of performance. A new timing-driven partitioning-based placement and detailed routing tool for 3D FPGA integration is developed and it is shown that 3D integration results in significant delay and wire length reduction for FPGA designs.

# **Contents**

| 1 INT                        | RODUCTION                                          | 1                    |

|------------------------------|----------------------------------------------------|----------------------|

| <b>1.1</b><br>1.1.1<br>1.1.2 | $\mathbf{I}$                                       | 1<br>1<br>3          |

| 1.2                          | Research Approach and Contributions                | 6                    |

| 1.4                          | Dissertation Outline                               | 9                    |

| 2 PRI                        | ELIMINARIES                                        | 11                   |

| 2.1                          | Introduction                                       | 11                   |

| 2.2                          | Partitioning                                       | 15                   |

| 2.3                          | Standard Cell Placement                            | 17                   |

| 2.4                          | Physical Design for FPGAs                          | 20                   |

| 2.5                          | Summary                                            | 23                   |

| 3 ST/                        | ATISTICAL TIMING-DRIVEN PARTITIONING AND PLACEMENT | 24                   |

| 3.1.1<br>3.1.2<br>3.1.3      | Previous Work                                      | 24<br>24<br>25<br>27 |

| 3.2                          | Statistical Timing Analysis                        | 27                   |

| 3.3                          | Statistical Timing-driven Partitioning             | 31                   |

| 3.4                          | Simulation Results                                 | 34                   |

| 3.5                          | Partitioning-based Placement                       | 35                   |

| 3.6                          | Summary                                            | 38                   |

| 4.1                                                                            | Introduction                                                                                                                                                                                                                       |  |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 4.1.1                                                                          |                                                                                                                                                                                                                                    |  |

| 4.1.2                                                                          | ***                                                                                                                                                                                                                                |  |

| 4.2                                                                            | Multi-objective hMetis Partitioning: Cutsize and Delay Minimization                                                                                                                                                                |  |

| 4.3                                                                            | Path-based Timing-driven Partitioning                                                                                                                                                                                              |  |

| 4.3.1<br>4.3.2                                                                 | G C C C C C C C C C C C C C C C C C C C                                                                                                                                                                                            |  |

| 7.5.2                                                                          | Algorum Delaus                                                                                                                                                                                                                     |  |

| 4.4                                                                            | Simulation Setup and Results                                                                                                                                                                                                       |  |

| 4.4.1<br>4.4.2                                                                 | 1                                                                                                                                                                                                                                  |  |

| 4.4.2                                                                          | Simulation Results                                                                                                                                                                                                                 |  |

| 4.5                                                                            | Partitioning-based Placement                                                                                                                                                                                                       |  |

| 4.6                                                                            | Summary                                                                                                                                                                                                                            |  |

|                                                                                | Introduction                                                                                                                                                                                                                       |  |

| 5.1.1                                                                          | Motivation                                                                                                                                                                                                                         |  |

| 5.1.1                                                                          | Motivation Previous Work                                                                                                                                                                                                           |  |

| 5.1.1<br>5.1.2<br>5.1.3                                                        | Motivation Previous Work                                                                                                                                                                                                           |  |

| 5.1.1<br>5.1.2<br>5.1.3<br><b>5.2</b>                                          | Motivation Previous Work Research Approach                                                                                                                                                                                         |  |

| 5.1.2                                                                          | Motivation Previous Work Research Approach Predictability Analysis                                                                                                                                                                 |  |

| 5.1.1<br>5.1.2<br>5.1.3<br><b>5.2</b><br><b>5.3</b><br><b>5.4</b>              | Motivation Previous Work Research Approach  Predictability Analysis  Robustness Analysis                                                                                                                                           |  |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.2<br>5.3                                          | Motivation Previous Work Research Approach  Predictability Analysis  Robustness Analysis  Case Study: Partitioning-based Placement                                                                                                 |  |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                     | Motivation Previous Work Research Approach  Predictability Analysis  Robustness Analysis  Case Study: Partitioning-based Placement  Simulation Results                                                                             |  |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>6 PLA            | Motivation Previous Work Research Approach  Predictability Analysis  Robustness Analysis  Case Study: Partitioning-based Placement  Simulation Results  Summary                                                                    |  |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.2<br>5.3<br>5.4<br>5.5<br>6 PLA<br>6.1.1          | Motivation Previous Work Research Approach  Predictability Analysis  Robustness Analysis  Case Study: Partitioning-based Placement  Simulation Results  Summary  ACE AND ROUTE FOR 3D FPGAS  Introduction Motivation               |  |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.2<br>5.3<br>5.4<br>5.5<br>6.1<br>6.1.1<br>6.1.2   | Motivation Previous Work Research Approach  Predictability Analysis  Robustness Analysis  Case Study: Partitioning-based Placement  Simulation Results  Summary  ACE AND ROUTE FOR 3D FPGAS  Introduction Motivation Previous Work |  |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.2<br>5.3<br>5.4<br>5.5<br>6 PLA<br>6.1.1          | Motivation Previous Work Research Approach  Predictability Analysis  Robustness Analysis  Case Study: Partitioning-based Placement  Simulation Results  Summary  ACE AND ROUTE FOR 3D FPGAS  Introduction Motivation Previous Work |  |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.2<br>5.3<br>5.4<br>5.5<br>6 PLA<br>6.1.1<br>6.1.1 | Motivation Previous Work Research Approach  Predictability Analysis  Robustness Analysis  Case Study: Partitioning-based Placement  Simulation Results  Summary  ACE AND ROUTE FOR 3D FPGAS  Introduction Motivation Previous Work |  |

| 5.3                                            | Placement Algorithm                                                                                                                                                                           | 83                                     |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

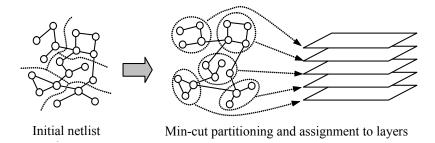

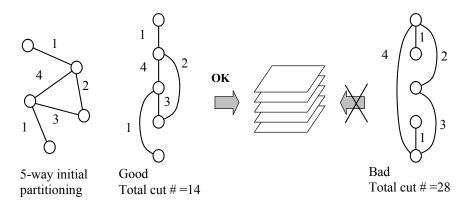

| 6.3.1                                          | Initial Partitioning and Assignment to layers                                                                                                                                                 | 83                                     |

| 6.3.2                                          | Placement Method                                                                                                                                                                              | 87                                     |

| 5.4                                            | Routing Algorithm                                                                                                                                                                             | 89                                     |

| 6.4.1                                          | Description of Detailed Routing Algorithm                                                                                                                                                     | 89                                     |

| 6.4.2                                          | Computation of Total and Foot-print Area                                                                                                                                                      | 92                                     |

| 6.5                                            | Simulation Results                                                                                                                                                                            | 93                                     |

| 6.5.1                                          | 3D Architectures                                                                                                                                                                              | 93                                     |

| 6.5.2                                          | Delay Results of TPR                                                                                                                                                                          | 95                                     |

| 6.5.3                                          | Wire Length Results of TPR                                                                                                                                                                    | 99                                     |

| 6.5.4                                          | Experiments Using Mixed Partitioning- and SA- based Placement Algorithm                                                                                                                       | 103                                    |

|                                                | Cummour                                                                                                                                                                                       | 106                                    |

| 5.6                                            | Summary                                                                                                                                                                                       | 100                                    |

|                                                | CLUSIONS AND FUTURE WORK                                                                                                                                                                      | 107                                    |

| 7 CON                                          |                                                                                                                                                                                               |                                        |

| 7 CON                                          | CLUSIONS AND FUTURE WORK                                                                                                                                                                      | 107                                    |

| 7 CON                                          | ICLUSIONS AND FUTURE WORK  Dissertation Summary  Future Work                                                                                                                                  | <b>107</b>                             |

| 7 CON 7.1 7.2 7.2.1                            | ICLUSIONS AND FUTURE WORK  Dissertation Summary  Future Work                                                                                                                                  | 107<br>107<br>108                      |

| 7 CON 7.1 7.2 7.2.1                            | CLUSIONS AND FUTURE WORK  Dissertation Summary  Future Work  Multi-objective Optimization Robust Design under Uncertainty                                                                     | 107<br>107<br>108<br>108               |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3          | CLUSIONS AND FUTURE WORK  Dissertation Summary  Future Work  Multi-objective Optimization Robust Design under Uncertainty                                                                     | 107<br>107<br>108<br>108<br>109        |

| 7 CON<br>7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3 | CLUSIONS AND FUTURE WORK  Dissertation Summary  Future Work  Multi-objective Optimization Robust Design under Uncertainty Architectural Studies and Efficient CAD Support for 2D and 3D FPGAs | 107<br>107<br>108<br>108<br>109<br>110 |

# **List of Tables**

| Table 1 Partitioning simulation results. Delay is computed using static timing analysis.              | 14     |

|-------------------------------------------------------------------------------------------------------|--------|

| Table 2 Placement simulation results. Delay is computed using static timing analysis. Simulations w   | ere    |

| performed on the same machine as those in Section 3.4.                                                | 16     |

| Table 3 Comparison between our methods and pure hMetis.                                               | 37     |

| Table 4 Timing driven partitioning placement vs. min-cut driven partitioning placement.               | 56     |

| Table 5 Comparison of the proposed placement algorithm to the classic net-based timing-driven         |        |

| partitioning-based placement. Delay is the delay reported by a static timing analysis algorithm       | and    |

| Standard deviation is the standard deviation of the overall circuit delay after placement (the        |        |

| smaller it is the more predictable is the circuit). Delay-change is the change in static delay afte   | er the |

| placement is changed in scenarios 1 or 2 (smaller means circuit more robust).                         | 40     |

| Table 6 Simulated circuits: statistics, vertical channel width (VCW) for successful routing, and run- | time   |

| (TPR compiled with $g++$ on a Linux box running on a Xeon 2.54GHz with 2G of memory).                 | 104    |

| Table 7 Average (of all circuits) of Delay, wire-length (WL), horizontal channel width (HCW), and     |        |

| routing area after successful routing for Sing-Seg architecture.                                      | 105    |

| Table 8 Average (of all circuits) of Delay, wire-length (WL), horizontal channel width (HCW), and     |        |

| routing area after successful routing for Multi-Seg architecture.                                     | 105    |

# **List of Figures**

| Figure 1 Variation of chip capacity and designer productivity give rise to the productivity gap            |     |

|------------------------------------------------------------------------------------------------------------|-----|

| (source: NTRS97).                                                                                          | 2   |

| Figure 2 Interconnect delay dominance as technology advances (source ITRS 2002).                           | 3   |

| Figure 3 Schematic diagram of a typical design process.                                                    | 4   |

| Figure 4 Y chart also known as Gajsky's Y chart [41].                                                      | 12  |

| Figure 5 Typical design flow.                                                                              | 13  |

| Figure 6 Steps during a typical PD cycle.                                                                  | 14  |

| Figure 7 Diagram depicting design styles.                                                                  | 17  |

| Figure 8 Illustration of standard cell placement.                                                          | 18  |

| Figure 9 Design styles comparison.                                                                         | 20  |

| Figure 10 (a) Typical symmetric array FPGA (b) Subset switch block.                                        | 21  |

| Figure 11 (a) Illustration of controlling pass transistors and multiplexers (b) Three-input LUT.           | 22  |

| Figure 12 (a) Circuit example (b) Placement on symmetric array FPGA.                                       | 23  |

| Figure 13 A sample circuit.                                                                                | 29  |

| Figure 14 (a) Associated DAG with shown criticalities; the most critical hyperedge {8, 9, 10} is cut       |     |

| Partitioning 1 (b) Partitioning 2 does not cut the most critical hyperedge; therefore, circuit de          |     |

| is smaller.                                                                                                | 29  |

| Figure 15 Voltage at the output of G6 (vertex 11 in Figure 14.b).                                          | 31  |

| Figure 16 (a) Schematic diagram of the proposed algorithm (b) Recursive bipartitioning tree, which         | eh. |

| illustrates bipartitioning levels.                                                                         | 32  |

| Figure 17 Statistical timing-driven partitioning.                                                          | 33  |

| Figure 18 Simulation setup.                                                                                | 35  |

| Figure 19 Example of a situation when net-based partitioning approaches fail to differentiate              |     |

| partitionings with the same cutsize but different delays.                                                  | 42  |

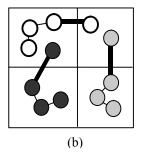

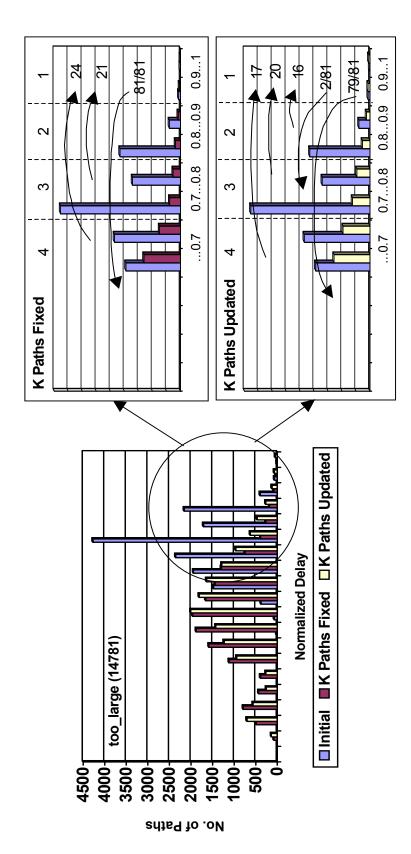

| Figure 20 The path delay distribution for <i>too large</i> (total number of paths is 14781) before and aft | er  |

| partitioning, which is done with and without updating the most critical paths in region 1 (0.9             |     |

| 1].                                                                                                        | 47  |

| Figure 21 Path delay distribution when $K$ most critical paths are updated or not illustrates the dela     | ay  |

| improvement obtained when K most critical paths are updated for too large.                                 | 49  |

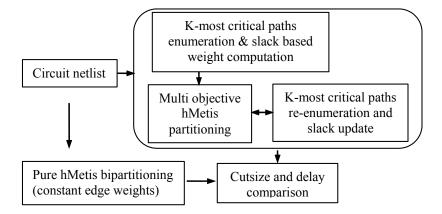

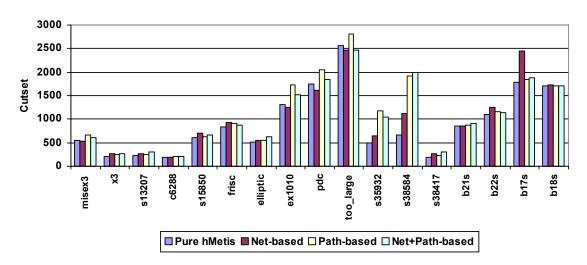

| Figure 22 Simulation setup for comparison of our proposed multi-objective hMetis partitioning              |     |

| algorithm to pure hMetis algorithm.                                                                        | 51  |

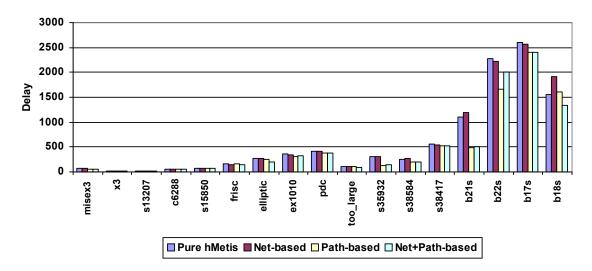

| Figure 23 Delay results comparison.                                                                        | 55  |

| Figure 24 Cutsize results comparison.                                                                      | 55  |

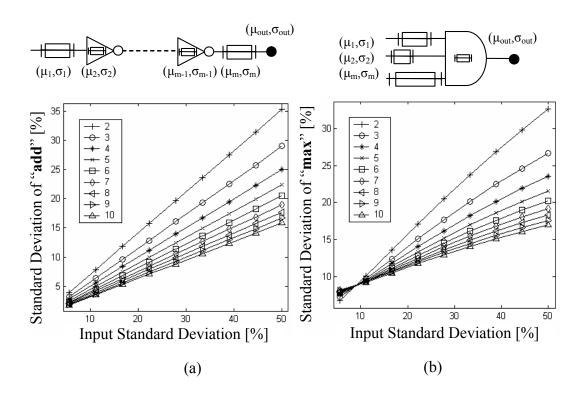

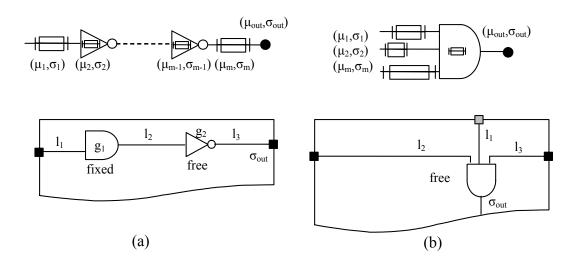

| Figure 25 (a) Standard deviation at the output $\sigma_{out}$ of a series of m delay elements (b) Standard |     |

| deviation at the output of a gate with <i>m</i> inputs                                                     | 63  |

| Figure 26 Study cases.                                                                                     | 64  |

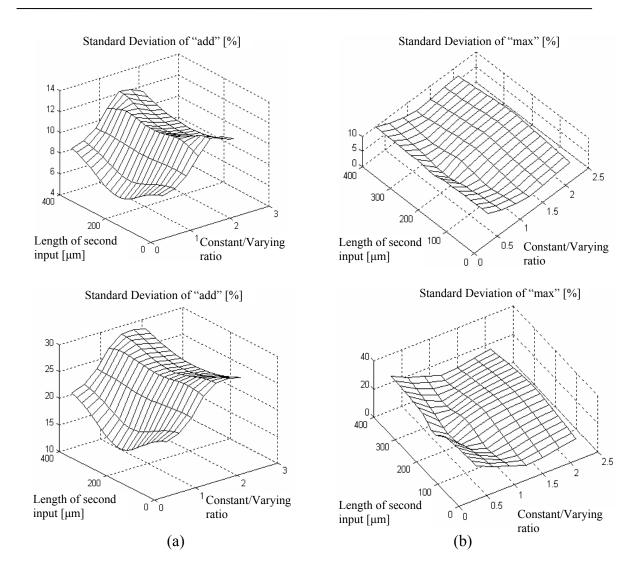

| Figure 27 Standard deviation when one delay element increases and another decreases for a) a ser           | ies |

| of delay elements and b) delay elements as LATs gate inputs. The x axis represents the varying             | ng  |

| length $l_2$ and the y axis is the ratio between the sum of means of fixed elements over the sum           | of  |

| varying means. Default standard deviation of all delay elements is 10% (top) or 25% (botton                | n). |

|                                                                                                            | 66  |

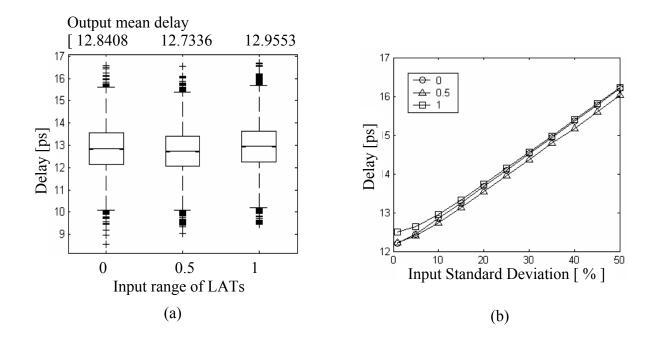

| Figure 28 (a) Average output delay of a three-input gate with input LAT range of 0, 0.5, and 1 (b)         |     |

| Average cell delay for the combination of the control factor with the noise factor.                        | 69  |

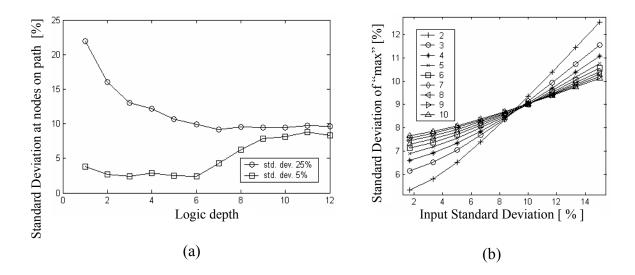

| Figure 29 (a) Standard deviation of LATs at nodes on critical path for <i>too_large</i> for 25% and 5%     |     |

| standard deviation for wire and gate (b) Enlarged bottom-left corner of Figure 25.b.                       | 72  |

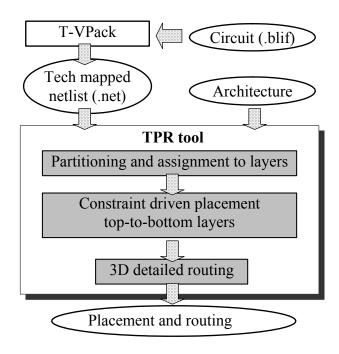

| Figure 30 Flow diagram of TPR: 3D placement and routing tool.                                      | 82        |

|----------------------------------------------------------------------------------------------------|-----------|

| Figure 31 Pseudo-code of TPR placement algorithm.                                                  | 83        |

| Figure 32 Illustration of initial partitioning and assignment to layers.                           | 84        |

| Figure 33 Illustration of good and bad initial linear placement of partitions into layers.         | 84        |

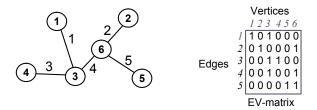

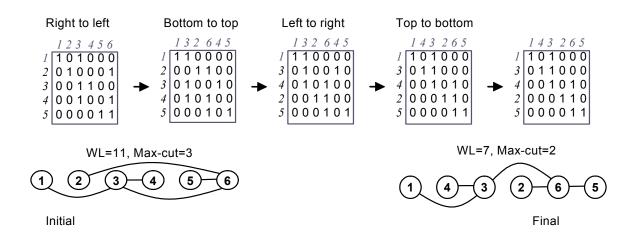

| Figure 34 Layer-blocks graph and its associated EV-matrix.                                         | 85        |

| Figure 35 Illustration of the EV-matrix band-width minimization for both wire-length and ma        | ximum     |

| cut between adjacent layers.                                                                       | 87        |

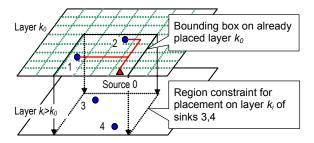

| Figure 36 Illustration of the restricted placement-region (i.e., projection of the bounding box    | of        |

| terminals 0, 1, and 2 placed on layer $k_0$ ) acting as a region constraint for sinks 3, 4 of a c  |           |

| net, which has the source and sinks 1, 2 placed on a layer above.                                  | 88        |

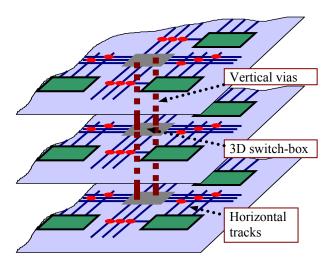

| Figure 37 Illustration of key elements of a 3D architecture; routing resources are horizontal t    | racks     |

| and vertical vias.                                                                                 | 89        |

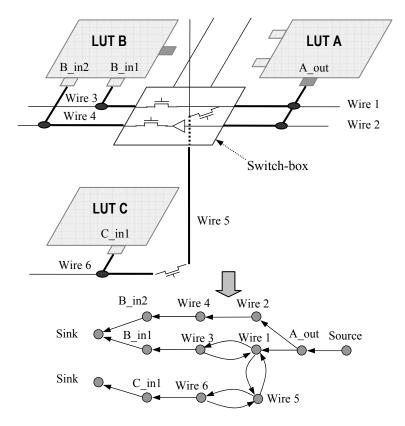

| Figure 38 Illustration of the routing graph construction.                                          | 90        |

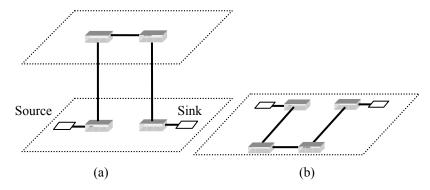

| Figure 39 Illustration of two routings for a two terminal net.                                     | 91        |

| Figure 40 Pseudo-code of TPR routing algorithm.                                                    | 91        |

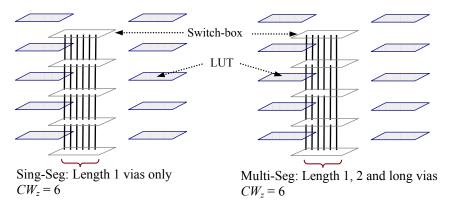

| Figure 41 Two different architectures used for simulations: Sing-Seg and Multi-Seg.                | 95        |

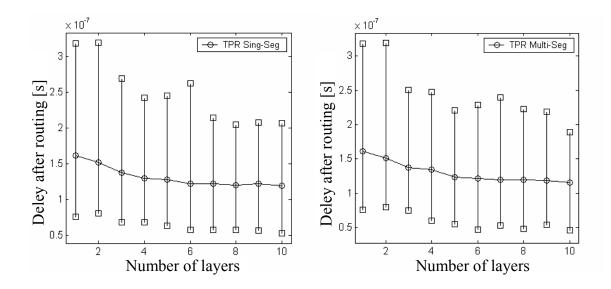

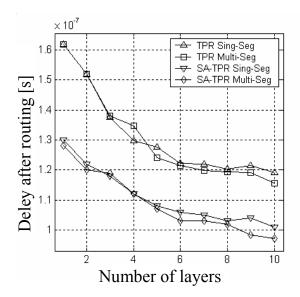

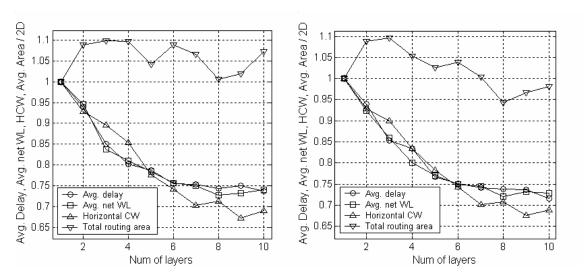

| Figure 42 Circuit delay after detailed routing as a function of number of layers for both          |           |

| architectures: Sing-Seg (left) and Multi-Seg (right).                                              | 97        |

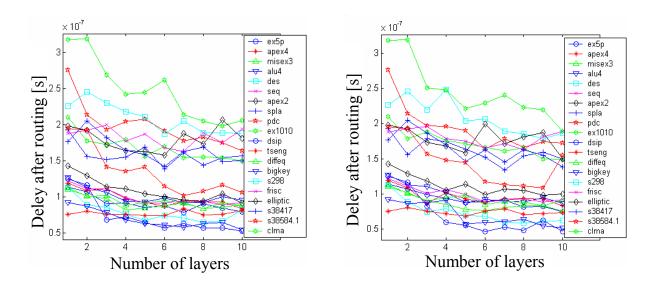

| Figure 43 Actual circuit delay variations for both architectures: Sing-Seg (left) and Multi-Seg    | (right).  |

| TPR is used for placement.                                                                         | <b>97</b> |

| Figure 44 Variation of delay as reported after detailed routing for placements obtained using      | our       |

| TPR and SA-TPR of [68].                                                                            | 98        |

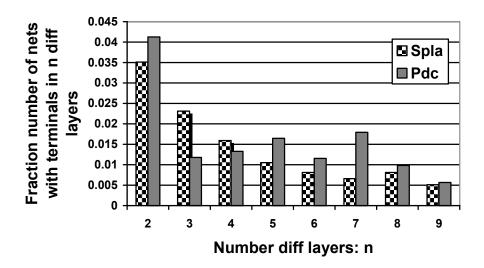

| Figure 45 Fraction (relative to number of nets with terminals in only one layer) of nets with te   | erminals  |

| in n different layers for two circuit-benchmarks.                                                  | 99        |

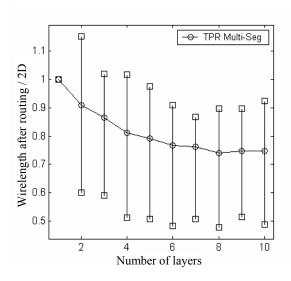

| Figure 46 Variation of wire-length, normalized to 2D case, as reported after detailed routing.     | TPR is    |

| used for placement.                                                                                | 100       |

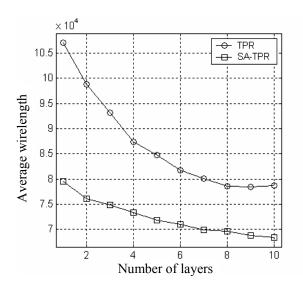

| Figure 47 Variation of average wire-length after detailed routing as a function of number of la    | ayers,    |

| using both TPR and SA-TPR [68] placement algorithms.                                               | 100       |

| Figure 48 Third dimension adds vertical tracks which require five connections.                     | 102       |

| Figure 49 Variations of the average delay, average net wire-length, horizontal channel width,      | and of    |

| total routing area for Sing-Seg (left) and Multi-Seg (right) architectures normalized rela         | tive to   |

| 2D, using TPR placement algorithm.                                                                 | 103       |

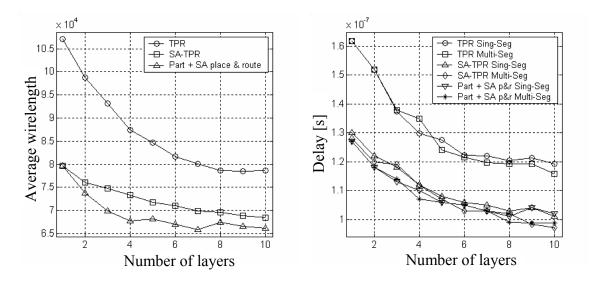

| Figure 50 Variation of average wire-length as estimated after placement and as reported after      | •         |

| detailed routing, using partitioning-, SA-, and mixed partitioning + SA- based placemen            |           |

| algorithms (left) and variation of delay as reported after detailed routing (right).               | 104       |

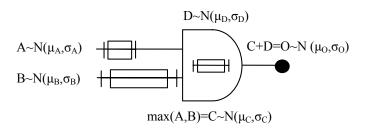

| Figure 51 Illustration of statistical "max" and "add" operations.                                  | 123       |

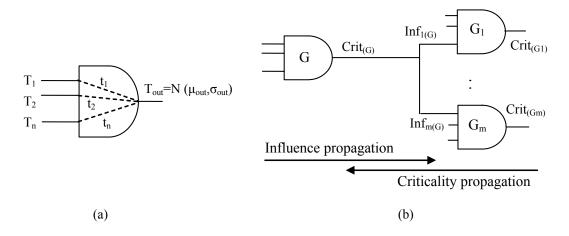

| Figure 52 (a) Example of general gate (b) Influence and criticality computation.                   | 125       |

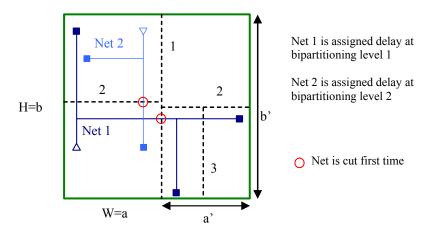

| Figure 53 Illustration of the wire delay assignment to cut nets at different bipartitioning levels | s. 129    |

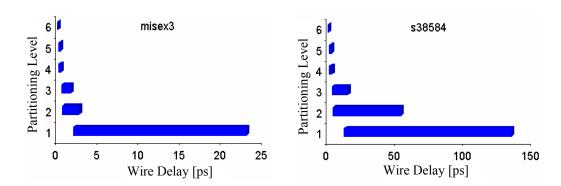

| Figure 54 Typical [min, max] delays assigned to cut nets at different bipartitioning levels. The   |           |

| level of partitioning (e.g. 1st level) the larger is the assigned delay.                           | 130       |

|                                                                                                    |           |

## 1 Introduction

#### 1.1 Motivation

#### 1.1.1 General Perspective

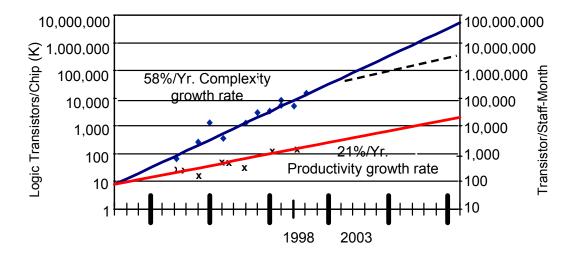

The continuous advance – at exponential pace – of technology for more than three decades facilitated the implementation of very complex and fast designs. This progress has followed Moore's law (which says that the number of transistors on a chip doubles roughly every two years) with incredible accuracy. For example, currently, Intel's fastest Pentium 4 chip clocks in at 3.2 GHz and has about 55 million transistors whereas chips containing 1 billion transistors – could be running at 10 GHz – will hit the market in 2007. However this progress has come at a cost and has been accompanied by unexpected difficulties, emerged due to miniaturization. One such difficulty is the productivity gap, depicted in Figure 1, which is a result of the faster increase of circuit complexities compared to the increase in designer productivity; the latter mainly taking place due to improved, more efficient CAD tools and bigger computational power. This problem is far from being solved and today fewer and fewer companies can close this gap, and when that happens, larger and larger design, test, verification and manufacturing teams are required.

Figure 1 Variation of chip capacity and designer productivity give rise to the productivity gap (source: NTRS97).

Furthermore, due to the non-uniform scaling of transistors and interconnects, previously ignored perturbations – such as process variations, temperature, and supply voltage changes – have become major design challenges because of their significant negative impact on the predictability of classic design methodologies, as well as on performance. New design techniques and CAD support, which shall lead to more robust designs and more predictable design methodologies, is needed.

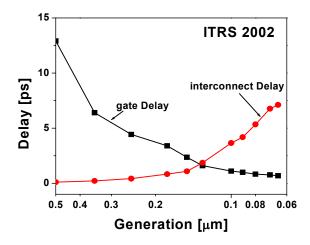

Moreover, due to the continuously increased chip sizes and transistor scaling, interconnect delay has become the dominant factor in determining circuit speed as illustrated in Figure 2. This problem can be partially alleviated using buffer insertion or pipelining techniques but is also far from being solved.

Figure 2 Interconnect delay dominance as technology advances (source ITRS 2002).

#### 1.1.2 A Closer Look

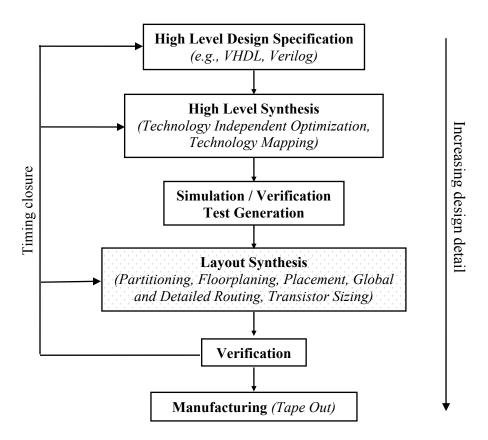

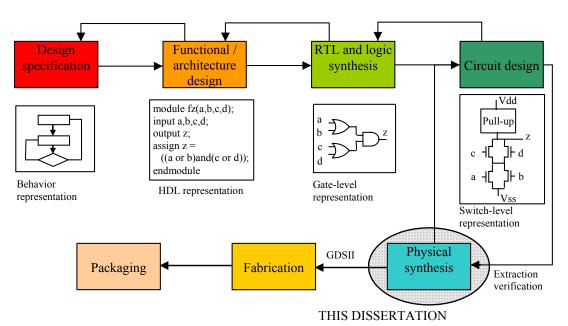

A typical design flow model is shown in Figure 3. The process of going from design specification to silicon implementation can be viewed as one of successive refinement, from the initial specification and register-transfer level (RTL) implementation to a logic level representation, via high level logic synthesis, followed by physical synthesis and design verification. This refinement is an entire collection of various optimization techniques, which pursue specific objectives, such as minimizing circuit delay (i.e., improving performance), power consumption or chip area or improving design reliability, as well as predictability.

After the last stage, if the design objectives are met, the design can be manufactured (i.e., fabricated in silicon). Nevertheless, if the design objectives (performance being the most important most often) are not met, the design process has to loop back to previous stages, and try to correct the problem, by either re-implementing parts of the design or re-optimizing it. In this

way, depending on the stage the design process loops back to, a number of design steps have to be repeated, with no guarantee of meeting the design objectives. If the problem to be corrected is small, then the design process will loop back to one of the back-end design stages, such as placement or routing. At later design stages, the design detail increases and more information about the final circuit structure and more accurate modeling techniques are available, which makes the evaluation of different cost functions more reliable and the whole design methodology more predictable. However, the impact of various optimization decisions at later design stages is smaller compared to the impact, which decisions made at higher levels can have. Therefore when the design objectives are not met by a big margin the design process will loop back to early, front-end, design stages.

Figure 3 Schematic diagram of a typical design process.

This design cycle is expensive, and can lead to significant delays in the time to market of a product. With such a scenario, it is obvious that the methodology described in Figure 3 is problematic. The designer needs to know how well the design is going to perform in its final form, but for that, information from later stages of the design process is needed. At early design stages the information about the final design is vague and therefore predictions on how the final design will perform are inaccurate. The impact of optimization decisions can have drastically different consequences at later stages. These consequences are not apparent when the choices are made, and at later stages, when the consequences are apparent, it is too expensive to go back and change the initial decision. The uncertainty introduced by variations due to process variations and temperature/voltage changes does only worsen the entire design process. Relying only on optimization approaches that consider only the gate delay is not desirable because in current technologies the wire delay is dominant, accounting for more than 70% of the total circuit delay [75]. One way to solve this dilemma is to try to elevate more information about the final design to the level of early design stages. This can be done by either adopting new design methodologies, such as platform-based design [87], or, as we propose in this thesis, by improving the estimation of various design metrics and integrating them into efficient algorithms, which shall be better aware of the later stages and the final implementation. Because of the continuously increasing circuit sizes, most of the wire delay is due to global interconnects (i.e., spanning multiple modules). A possible solution to this problem is to adopt 3D integration. 3D integration could significantly reduce wire-lengths, boost yield, and could particularly be useful for FPGA fabrics because it could address problems related to routing congestion, limited I/O connections, and

long wire delays. Practical application of 3D integrated circuits yet needs to gain momentum, partly due to a lack of efficient 3D CAD tools.

The research presented in this dissertation is aimed directly at the problems discussed so far. We develop (1) improved partitioning algorithms that can be embedded in partitioning based placement tools (divide and conquer approach suitable for the increasing circuit sizes) which lead to improvements in circuit delay, (2) an analysis methodology to better understand the relationship between robustness, predictability and performance of VLSI circuits and techniques to gear a standard timing-driven partitioning-based placement algorithm to design more predictable and robust circuits without sacrificing much of performance, (3) a placement and detailed routing tool for 3D FPGAs, which is used to explore potential benefits in terms of performance and area that future 3D integration technologies can achieve.

#### 1.2 Research Approach and Contributions

The increase in circuit complexities and the high demand for short time-to-market products force designers to adopt divide-and-conquer and platform-based design methodologies. Furthermore, ever-growing performance expectations require designers to perform optimization at all levels of the design cycle. Significant contribution of interconnect to the area and delay of today's and future chips, combined with the fact that partitioning and placement have a great impact on the interconnect distribution, makes partitioning and placement very important steps during physical design. It is imperative to account for timing during these design steps to allow for early wire planning. In the first part of this dissertation, we address the problem of delay optimization at the physical design stage. A new net-based statistical timing-driven partitioning algorithm demonstrates that circuit delay can be improved while the run-time remains virtually

the same and the cutsize deterioration is insignificant [3]. Path-based timing-driven partitioning has the advantage that global information about the structure of the circuit is captured. We propose multi-objective partitioning for cutsize and circuit delay minimization [1], [2]. We change the partitioning process itself by introducing a new objective function that incorporates a truly path-based delay component for the most critical paths. To avoid non-critical paths from becoming critical, the traditional slack-based delay component is also accounted for. The proposed timing-driven partitioning algorithm is built on top of the hMetis algorithm, which is very efficient. Integration of our partitioning algorithms into a leading-edge placement tool demonstrates the ability of the proposed edge-weighting and path-based approaches for partitioning to lead to a better circuit performance.

A design methodology should offer predictable and robust designs at the best performance. High robustness means that performance of the design is less influenced by noise factors and remains within acceptable limits. The design methodology should also be predictable. Predictability is to be achieved in the face of design uncertainties, which are caused by either incomplete system specification or inherent difficulty of estimating performance metrics during the optimization process. In the second part of this dissertation we analyze the relationship between robustness, predictability and performance (optimality) and seek means for their control. We apply our techniques to timing-driven partitioning-based placement algorithm in order to design more predictable and robust circuits without sacrificing much of performance [4]. We regard the optimization process under uncertainty as the iterative computation of a number of objective functions, which depend on variables whose values are known within a range of values (i.e., as probability distributions or as intervals within which these variables lie). In this context, predictable design means the ability to accurately compute the objective function (within the

chosen modeling framework), and to find means of making current estimations closer to the real final values. We use the standard deviation as the measure of predictability of the overall circuit delay distribution at the primary outputs, as well as at the output of each cell inside the circuit. This means that the smaller the standard deviation, the more predictable is the delay. The slope of the variation of the standard deviation of the overall circuit delay, when gate and wire delays change, characterizes the robustness of the circuit.

The potential impact of practical application of 3D integration for FPGAs is currently unclear partly due to a lack of efficient 3D CAD tools. In the third part of this dissertation our goal is to present an efficient placement and detailed routing tool for 3D FPGAs. Unlike previous works on 3D FPGA architecture and CAD tools, we investigate the effect of 3D integration on delay, in addition to wire-length because wire-length alone cannot be relied on as a metric for 3D integration benefits. Apart from the commonly used single-segment architecture, we also study multi-segment architectures in the third dimension. Our placement algorithm is partitioning-based, and hence scalable with the design size. We show that 3D integration can result in smaller circuit delay and wire-length.

The research presented in this dissertation can be seen as only the beginning of longer term endeavors with future directions discussed in the last chapter. Nevertheless, it still has produced some worthwhile results, which can be summarized as main contributions as follows:

• New timing-driven partitioning algorithms: The use of statistical timing criticality concept to change the partitioning process itself (classified as a net-based partitioning approach), on one hand, and the use of a new objective function that incorporates a truly path-based delay component for the most critical paths (classified as path-based

approach), on the other hand, proved to lead to performance improvement at both partitioning and placement level.

- Better understanding of the relation between robustness, predictability, and performance: At the partitioning and placement levels of abstraction we have built a modeling framework, which allowed us to explore for the first time ways of performing physical design to achieve more predictable and robust circuits without sacrificing much of performance.

- TPR (Three-dimensional Place and Route): We have developed a partitioning-based placement and detailed routing toolset. We have used it as a platform in performing architectural analysis in order to analyze potential benefits that 3D integration can provide for FPGAs. More specifically, we have placed and detailed routed circuits onto 3D FPGA architectures and studied the variation in wire-length and, for the first time, in total circuit delay compared to their 2D counterparts. Our results can guide researchers in designing high performance 3D FPGA fabric architectures.

#### 1.4 Dissertation Outline

This dissertation is organized as follows. Chapter 2 is a general overview of physical design (PD) of VLSI circuits and FPGAs. It builds the background for the topics presented in the rest of this dissertation. The first part, encompassing Chapters 3 and 4, presents new partitioning algorithms (net based and path based) that can lead to circuit delay improvements both at the partitioning abstraction level and after they are embedded into a placement algorithm. The second part of this dissertation, spanning Chapter 5, investigates the relation between robustness, predictability, and performance. Chapter 6, which represents the third part of the dissertation, is

concerned with the presentation of a new placement and detailed routing tool used for exploration of 3D technologies. Conclusion and future research directions are presented in Chapter 7. Appendix A represents a detailed presentation of statistical timing analysis, which is used to build the modeling framework for the research in Chapter 3 and Appendix B discusses our delay modeling.

## 2 Preliminaries

#### 2.1 Introduction

This chapter is devoted to the presentation of physical design of VLSI circuits and FPGAs. The abbreviation VLSI stands for Very Large Scale Integration, which refers to integrated circuits that have more than 10<sup>5</sup> transistors. FPGA stands for Field Programmable Logic Arrays, which is a different design style described later in this chapter. We will present a rather general view of the basic design steps in a typical physical design phase in order to build the background for the topics presented in the rest of this dissertation.

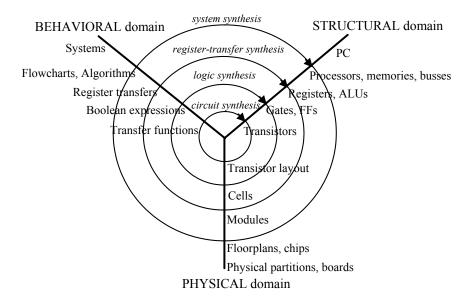

In dealing with the ever increasing complexity of integrated circuits the concepts of hierarchy and abstraction are helpful [41]. Hierarchy captures and shows the structure of a design at different levels of description whereas abstraction hides the lower level details. Abstraction makes it possible to reason about a limited number of interacting parts at each level in the hierarchy. Each part is, at its turn, composed of interacting subparts at a lower level of abstraction. This decomposition continues till the basic building blocks (e.g., transistors) of a VLSI circuits are reached. Because a single hierarchy is not enough to properly describe the VLSI process, there is a general consensus to define three design domains, each with its own hierarchy (see Figure 4). These domains are as follows [41]:

• The behavioral domain. The design or part of it is seen a black box and the relations between inputs and outputs are given with no reference to their implementations. For

example, a design with the complexity of a several transistors can be described using Boolean algebra equations or truth tables. At even higher levels of abstraction a design can be represented as interacting algorithms that will realize the computation described with no visible connection to hardware.

- The structural domain. The circuit is seen as the composition of subcircuits. A design description in this domain captures information on the subcircuits and their connectivity. For example, a schematic showing how gates are interconnected to implement some arithmetic unit represents a structural description at the gate abstraction level in this domain.

- The physical (or layout) domain. Descriptions in this domain give information on how the subparts that can be seen in the structural domain, are located on two (usually) dimensional plane. For example a cell that may represent the layout of a logic gate will consist of mask patterns which form the transistors of this gate and its interconnections.

Figure 4 Y chart also known as Gajsky's Y chart [41].

Apart from describing the three design domains in one picture, the Y-chart is a very powerful tool to illustrate different design methodologies. For example, a typical top-down design methodology (further illustrated in Figure 6) is described by an inward spiral path in Figure 4. Parts of the design with known behavior are decomposed into smaller blocks with simpler behavior and an interconnection structure. This corresponds with a transition from the behavioral to the structural domain. A transition step from the structural to the physical domain follows and this illustrates the fact that layout is taken into account during all design stages. Then, each subpart can be thought to be located on the behavioral axis and is decomposed at its turn. This inward spiral path continues until the circuit has been specified down to the lowest structural level (i.e., transistors).

Figure 5 Typical design flow.

Specification is a description of what the system does. During the design process the structure of the system is determined, using different methods to achieve a function and logical structures

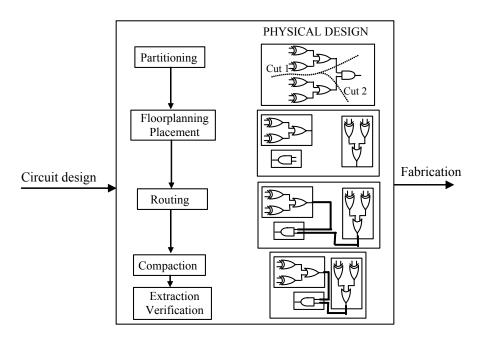

that perform the architecture. Realization (fabrication) materializes the physical structures in a certain technology (e.g., CMOS) using a design style (described shortly). Physical design basically converts a circuit description (resulted from logic synthesis) into a geometric description (GDSII file), which is used to manufacture a chip. A typical physical design cycle has the following steps (see Figure 6):

- Logic partitioning

- Floorplanning, placement, and pin assignment

- Routing (global and detailed)

- Compaction

- RLC extraction & verification

Figure 6 Steps during a typical PD cycle.

The main two steps of a typical PD flow are placement and routing. Partitioning can be used to first divide the circuit into smaller sub-circuits which can be optimized individually. Individual

solutions are put together to give the solution of the entire larger circuit. In this chapter we will first discuss partitioning and outline its role in PD for VLSI. We will then describe the placement problem mainly for standard cell as well as for FPGAs.

#### 2.2 Partitioning

Generally, partitioning is the decomposition of a complex system into smaller subsystems until each subsystem has manageable size. More formally, the partitioning process takes as input a graph or hypergraph, possibly with vertex (node) and/or edge (arc) weights and the objective is to assign nodes to partitions such that the cutsize (cutset) is minimized subject to constraints such as number of partitions (K-way partitioning) or maximum capacity of each partition, or maximum allowable difference between partitions.

Graph partitioning arises as a preprocessing step to divide-and-conquer algorithms, where it is often a good idea to break things into roughly equal-sized pieces. Several different flavors of graph partitioning arise depending on the desired objective function [79]:

- Minimum cutset The smallest set of edges to cut that will disconnect a graph can be

efficiently found using network flow methods. Since the smallest cutset can split off only

a single vertex, the resulting partition might be very unbalanced.

- Graph partition A better partition criterion seeks a small cut that partitions the vertices

into roughly equal-sized pieces. This problem is NP-complete [40] and many heuristics

have been proposed, which work well in practice.

- Maximum cut Given an electronic circuit specified by a graph, the maximum cut

defines the largest amount of data communication that can simultaneously take place in

the circuit. The highest-speed communications channel should thus span the vertex

partition defined by the maximum edge cut. Finding the maximum cut in a graph is NP-complete [36], [40].

The basic approach to dealing with graph partitioning or max-cut problems is to construct an initial partition of the vertices (either randomly or according to some problem-specific strategy) and then sweep through the vertices, deciding whether the size of the cut would increase or decrease if we moved this vertex over to the other side. The decision to move v can be made in time proportional to its degree by simply counting whether more of neighbors of v are on the same team as v or not. Of course, the desirable side for v will change if many of its neighbors jump, so multiple passes are likely to be needed before the process converges on a local optimum. Even such a local optimum can be arbitrarily far away from the global max-cut.

One of the most notable heuristics is the Kernighan-Lin (KL) algorithm [57] which was later improved by the Fiduccia-Mattheyses (FM) algorithm [39]. The KL algorithm is an iterative improvement technique and works on non-weighted graphs. It iterates as long as the cutsize improves: (i) Find a pair of vertices that result in the largest decrease in cutsize if exchanged, (ii) Exchange the two vertices (potential move), (iii) "Lock" the vertices, (iv) If no improvement possible, and still some vertices unlocked, then exchange vertices that result in smallest increase in cutsize. Its main drawbacks are: it finds balanced partitions only, it does not use weights for the vertices, it has high time complexity, it work only on edges, not hyper-edges.

The FM algorithm is a modified version of KL to mainly improve on the run-time. Among its main advantages is that it works with unbalanced partitions, introduces special data structure to improve time complexity, vertices can have weights, the concept of cutsize is extended to hypergraphs, and it can be extended to multi-way partitioning. Other partitioning algorithms include min-cut/max-flow, Ford-Fulkerson (for unconstrained partitions), ratio cut, genetic

algorithm, and simulated annealing. To cope with the increased size of graphs, multi-level approaches have been proposed [56], [30], [13].

Within the context of PD for VLSI, partitioning is used to divide the circuit (represented as a graph) into sub-circuits (sub-graphs) of smaller size, which can be handled easier individually. Most often, partitioning is closely connected to the placement process. Placement can be done by recursive bipartitioning or quadrisection (see next chapters) with local refinement techniques, which use usually simulated annealing. Analytic placers such as Gordian [58] also use partitioning to assign nodes to different chip regions in order to partially remove overlaps and help convergence to a stable solution. The traditional objective of partitioning used to be the cutsize. However, in the context of design automation for VLSI, the cost function of the partitioning process need be augmented with delay components. This means that delay is optimized early during the design cycle where optimization decisions can be made easier and can lead to a better wire-planning, which eventually can reduce the design cycles. Ways of including delay into the partitioning optimization process will be described in the next two chapters.

#### 2.3 Standard Cell Placement

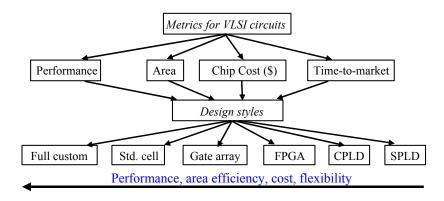

The main circuit design styles (methodologies) are described in Figure 7.

Figure 7 Diagram depicting design styles.

The *full custom* approach uses hand-crafted functional and physical blocks. Because the number of such blocks is relatively small the placement problem size is rather relatively small and becomes a floorplanning problem (macro-cell placement). The efforts and costs of this design style are high and therefore high quality and high production volume are expected. The *standard cell* design methodology uses cells (such as OR, NAND, XOR, etc.), which are characterized and stored in libraries. The placement of cells on the chip area is performed on rows. Cell rows are spaced to leave extra room for routing, which is usually done using up to eight-nine metal layers. An example of a standard cell placement is shown in Figure 8. These cells however need be updated when technology changes. The main advantage is that it is easy to develop CAD tools for design and optimization. Because the level of abstraction is relatively low, the placement problem size is large. Also, tremendous characterization effort (e.g., parameterized area and delay over ranges of temperatures and operating voltage) is needed.

Figure 8 Illustration of standard cell placement.

Apart from standard cells there can also be macro-cells (PLA, ALU, etc.) which need be placed. In this case the placement is called mixed standard cell and macro-cell placement. The

main optimization objective of standard cell placement algorithms used to be the total wirelength. The total wire-length represents the sum of lengths of each net in the circuit. At the placement level (when the exact routing of each net is not known yet) the wirelength of each net is commonly approximated by the half perimeter of the bounding box of all terminals of a net. However, due to the fact that with the advance of technology into deep submicron geometries, interconnects have become the dominant factor for the performance (delay) of a circuit. This leads to an increased importance of the placement design step where wire planning and performance optimization are treated as direct optimization goals because relying on wirelength optimization only may not be enough (a minimum total wire-length does not necessarily mean best circuit delay). The main standard cell placement approaches are as follows. (a) Constructive placement techniques are based on the idea of divide-and-conquer. They usually use bipartitioning or quadrisection to divide the problem into smaller problems, which can then be placed individually with a better placement technique such as branch-and-bound or simulated annealing. These approaches can be top-down when partitioning is used, or bottom-up when clustering is used to divide the problem into smaller, easier to handle, subproblems. This placement approach has the advantage of being scalable with the ever increasing circuit sizes while offering competitive solution quality. Most of the ideas presented in following chapters adopt this placement approach. (b) Iterative methods usually are based on simulated annealing or force directed technique. They start with an initial placement and iteratively improve the wirelength and area. (c) Analytic placement algorithms formulate the placement as a constrained optimization problem where the objective is to minimize usually a quadratic in distance cost function. Well established quadratic solvers are employed to seek the numerical solution. The solution has overlapping cells which need be removed during a post processing step. Forcedirected placement algorithms seek placement solutions by searching cell locations with the best balance between attracting and repelling forces.

Gate array design style uses arrays which are pre-manufactured. Metal and contact layers are used to programm the chip. It has the advantage that fewer manufacturing steps correlate to lower fabrication time and cost. The CPLD/FPGA design style is described in the next section. Programmable logic devices (PLD) design style. Any logic function is implemented using two level logic embedded into two pre-fabricated arrays of AND and OR gates. A comparison between all the above design styles is presented in Figure 9.

|                | Full custom | Standard cell | Gate array | FPGA       | SPLD       |

|----------------|-------------|---------------|------------|------------|------------|

| Density        | Very high   | High          | High       | Medium     | Low        |

| Performance    | Very high   | High          | High       | Medium     | Low        |

| Flexibility    | Very high   | High          | Medium     | Low        | Low        |

| Design time    | Very long   | Short         | Short      | Very short | Very short |

| Manufacturing  | Medium      | Medium        | Short      | Very short | Very short |

| time           |             |               |            |            |            |

| Unit cost –    | Very high   | High          | High       | Low        | Very low   |

| small quantity |             |               |            |            |            |

| Unit cost –    | Low         | Low           | Low        | High       | Very high  |

| large quantity |             |               |            |            |            |

Figure 9 Design styles comparison.

#### 2.4 Physical Design for FPGAs

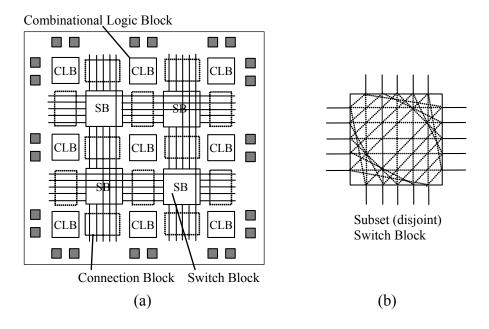

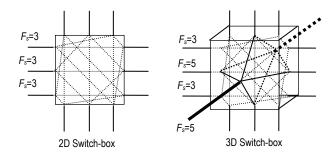

FPGAs are arrays of programmable modules with the capability of implementing any generic logic function. Wires (routing segments) can be connected by programmable connections inside switch blocks (SBs) and connection blocks (CBs). A typical (Xilinx XC4000 like) FPGA array is shown in Figure 10.

Figure 10 (a) Typical symmetric array FPGA (b) Subset switch block.

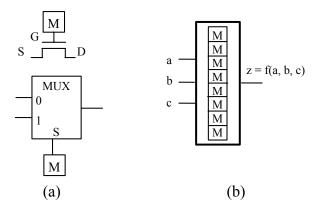

The logic (i.e., functionality) is implemented using memory look-up tables (LUTs - located at fixed locations on the chip), which together with other "gluing" logic (multiplexers, flip-flops, etc.) make-up combinational logic blocks (CLBs). A look-up table with *n* inputs can implement any Boolean function depending on *n* variables. An example of a LUT with three inputs (which means 8 entries in the table) is presented in Figure 11. A CLB can have more LUTs (clusters or LUTs) in hierarchical programmable fabrics. FPGAs have routing resources pre-fabricated and are uniform throughout the chip placed in horizontal and vertical channels. A channel can have more tracks, and each track can have routing segments of different lengths. Connections between routing segments are made using switch connections inside SBs while connections between LUTs and routing segments are done inside CBs. Connections are implemented using multiplexers and pass transistors. The advantage of FPGAs is that they reduce the development and production time and have low cost. The content of every LUT (implementing logic functions) as well as

information about what connections are on and off inside SB's and CB's is decided through a bitstream (loaded from a PROM after power on), which is loaded onto the FPGA. Part of this bitstream is the content of the LUTs themselves. The rest of it represents information which will be stored in SRAM cells, which control multiplexers and pass transistors (see Figure 11).

Figure 11 (a) Illustration of controlling pass transistors and multiplexers (b) Three-input LUT.

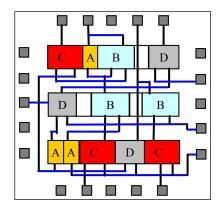

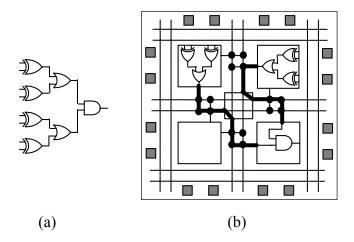

The placement and routing of a circuit implemented on FPGAs is essentially similar to the case of standard cell design style (see Figure 12). The main objective is usually the performance of the circuit. However performance (i.e., delay) is not directly proportional to the Manhattan distance as in the case of standard cell placement. Instead, the dominant factor is the number of routing segments used to route a net. Using more routing segments (i.e., more switch connections along the route) increases the delay because switches have large delays. Our goal, at placement level, is to place all the cells (which now are functions embedded into LUTs) such that the final wirelength and delay will be minimized and the circuit will be fully routable using a minimum number of routing tracks (which eventually will translate into minimum chip area) because in practice, pre-fabricated FPGA chips have limited routing resources.

Figure 12 (a) Circuit example (b) Placement on symmetric array FPGA.

#### 2.5 Summary

This chapter discussed physical synthesis as one of the main design steps in a typical design flow. Emphasis was put on presenting graph partitioning within the context of design automation for VLSI circuits. Placement for both VLSI circuits and FPGAs was presented as well. We thus built the basic theoretical framework for presenting our contributions in the next chapters.

# 3 Statistical Timing-driven

## **Partitioning and Placement**

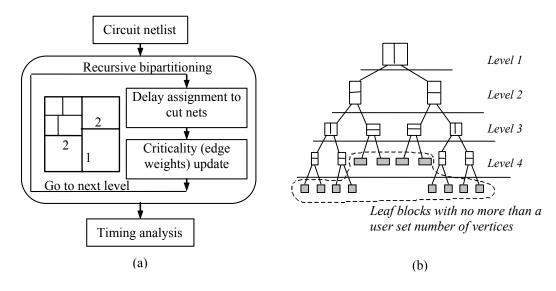

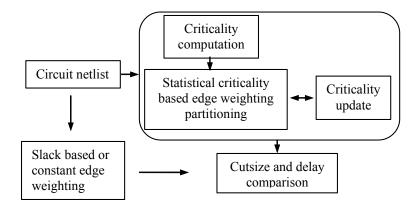

In this chapter, we present a method for statistical timing driven hMetis-based partitioning. We approach timing driven partitioning from a new perspective, compared to previous works: we use a statistical timing criticality concept to change the partitioning process itself. We exploit the hyperedge coarsening scheme of the hMetis partitioner for our timing minimization purpose. This allows us to perform partitioning such that the most critical nets in the circuit are not cut and therefore timing minimization can be achieved. The use of the hMetis partitioning algorithm makes our partitioning methodology faster than previous approaches. Simulations results show that 10% average delay improvement can be obtained. Furthermore, integration of our partitioning algorithm into a leading-edge placement tool demonstrates the ability of the proposed edge weighting approach for partitioning to lead to better circuit performance.

#### 3.1 Introduction

#### 3.1.1 Motivation

The increase in circuit complexities and the high demand for short time-to-market products force designers to adopt divide-and-conquer (partitioning-based placement tools attracted more

attention [92]) and platform-based design methodologies [87]. Furthermore, ever-growing performance expectations require designers to perform optimization at all levels of the design cycle. Significant contribution of interconnect to the area and delay of today's and future chips, combined with the fact that partitioning has a great impact on the interconnect distribution, makes it a very important early step during physical design. During this design step, it is imperative to account for timing in order to facilitate early wire planning. Partitioning is a divide-and-conquer approach that facilitates the decrease of the problem size to levels where each partition can be handled in realistic computational times. It is an early and very important step during the physical design process not only for the fact that it influences successor steps like placement, floorplanning, routing but also because it influences the overall performance of the circuit.

#### 3.1.2 Previous Work

Timing driven partitioning approaches can be classified into two categories: (1) top-down approaches and (2) bottom-up clustering-based approaches. Approaches in the first category are usually based on the Fiduccia-Mattheyses (FM) recursive min-cut partitioning method [39] or on quadratic programming formulations [72], [86]. Timing optimization is obtained by minimizing the delay of the most critical path. Approaches in the second category are bottom-up clustering-based approaches. They are used mostly as pre-processing steps for min-cut algorithms [24]. Most previous approaches achieve delay minimization by altering the netlist using logic replication, retiming, and buffer insertion in order to meet delay constraints while minimizing the cutsize. Gate replication in these methods can be massive. The way timing optimization is handled in timing-driven partitioning approaches can be classified into two categories: (1) path-based timing minimization approaches. Most

of the previous works fall into the second category. The idea of the path-based approaches is to find the K most critical paths<sup>1</sup> in the circuit and then make sure that the partitioning does not cut those paths or cuts them only a few times. That is obtained by assigning large weights to nets along these K critical paths using formulations that capture path slack and path connectivity. Timing minimization may be obtained because the most critical paths in a circuit determine the final delay of the circuit. The advantage of this approach is mainly that global information about the structure of the circuit is captured [37]. The disadvantage is that determining the best value of K is difficult. Too small a K may not result in any delay improvement as many paths initially declared as critical turn out not to be critical after placement and routing is done. Furthermore, paths identified as non-critical may become critical along the physical design steps. On the other hand, choosing a large value for K means longer run time and limited search space for the partitioning / placement process. Hence, K has to be large enough to enclose critical and semi-critical nets, but not too large to prohibitively slow down the physical design algorithms.

One can identify the following problems for previous timing driven partitioning approaches:

(i) Unrealistic delay models are used. Commonly, the *general-delay* model is used, which considers delay 1 for all gates, delay 0 for interconnects inside a partition, and a constant delay for interconnects between partitions [29], [67], [72]. (ii) Unrealistic simplifications are made. For instance, circuits are mapped to two-input gates only [29]. (iii) The run time for moderate-sized circuits is too long and makes previous approaches impracticable for large circuits. One reason for that may be that previous approaches usually separate the timing-driven partitioning into two steps: clustering or partitioning followed by timing refinement based on netlist alteration [29], [72].

<sup>&</sup>lt;sup>1</sup> The number of paths in a circuit is exponential with respect to the number of nodes in the worst case. Hence, for practical reasons we have to focus on the *K* top-most critical paths.

#### 3.1.3 Research Approach

In an attempt to correct the above drawbacks, we approach, in this chapter, timing driven partitioning using a statistical timing criticality concept to change the partitioning process itself such that delay minimization is achieved while delay uncertainties are considered [3]. We use a realistic delay model, which incorporates statistical net-length estimation. Furthermore, we employ the hMetis partitioning algorithm, which is very fast. For our timing minimization purpose, we exploit the hyperedge coarsening scheme of hMetis partitioner [56]. This allows us to perform partitioning such that the most critical nets in the circuit are not cut and therefore timing minimization can be achieved. Our approach is different from previous works in the sense that we do not alter the netlist (e.g., by performing buffer insertion and gate duplication). Instead, we perform the partitioning of the circuit carefully so that wire delays on the critical paths are minimized. Previous techniques that exploit methods like buffer insertion can follow our partitioning stage to further improve on circuit delay. By improving on timing by minimizing critical wire delays at partitioning level, we provide a way of performing wire planning very early in the physical design process. We validate the proposed timing-driven partitioning algorithm by integrating it into Capo [24], a well-known placement tool to demonstrate that the improvements from our partitioning method are sustained at the placement level as well.

## 3.2 Statistical Timing Analysis

We present the concept of criticality within the framework of statistical timing analysis versus static timing analysis. The idea of *static timing analysis* is to compute the slack for every gate based on the latest arrival time and the required arrival time values. Each gate has a constant

delay value. However, in reality there are several uncertainties in both gate and wire delays, such as fabrication variations, changes in supply voltage and temperature [44], [69], [85]. These uncertainties are modeled in *statistical timing analysis* (SSTA) by considering gate and wire delays as random variables (i.e., as probability distribution functions). That means that the delay variation is captured by the standard deviation. In the past, different statistical timing analysis models have been proposed [52], [63]. We adopt the approach proposed by Berkelaar [17], [50] for its simplicity and because it represents the formulation which appears in other recent statistical timing analysis techniques [9], [71]. Hashimoto and Onodera [44] introduced later the concept of *criticality*, which we use in our weighted min-cut partitioning framework. Delay distribution at primary outputs (POs) is obtained by computing the statistical latest arrival times. Statistical delays are forward-propagated from primary inputs (PIs) towards primary outputs, using *statistical* addition and maximum operations. Because it is not our main contribution and because it is also used in a later chapter of this thesis, a description of SSTA is provided in Appendix *A*.

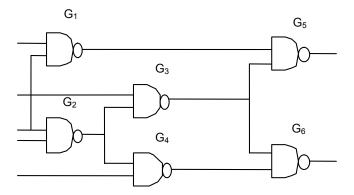

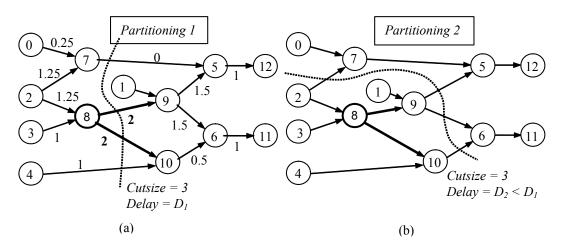

In what follows we present an example, which illustrates the difference between statistical (as described in Appendix *A*) and static edge weighting. As an example of the effect of criticality on circuit delay and its interaction with the partitioning process, consider the circuit of Figure 13. The hypergraph shown in Figure 14.a as a directed acyclic graph (DAG) depicts timing criticality (as defined in Appendix A and [44]) values for all hyperedges.

Figure 13 A sample circuit.

Gate  $G_2$  in the circuit schematic (i.e., vertex 8 in the corresponding DAG) and its fanout net (i.e., hyperedge  $\{8, 9, 10\}$  in DAG) is the most critical one with a criticality value of 2.

Figure 14 (a) Associated DAG with shown criticalities; the most critical hyperedge {8, 9, 10} is cut by *Partitioning 1* (b) *Partitioning 2* does not cut the most critical hyperedge; therefore, circuit delay is smaller.

If a traditional min-cut partitioning algorithm were used, then there would be no way of distinguishing between partitioning 1 (which cuts the most critical hyperedge) shown in Figure

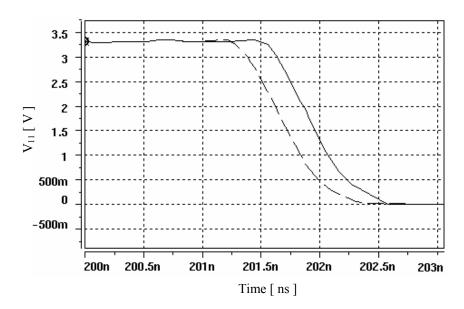

14.a and partitioning 2 shown in Figure 14.b. That is because both partitionings have the same cutsize of three. However, the circuit delay<sup>2</sup> is different for the two cases, as shown in Figure 15.